Classroom Model of an Information and Computing System

by

MICHAEL DAVID SCHROEDER

B. A., Washington State University

(1967)

SUBMITTED IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 1969

Signature of Author

Signature redacted

Department of Electrical Engineering,

January 20, 1969

Signature redacted

Phesis Supervisor

Signature redacted

Chairman, Departmental Committee on Graduate

Students

Archives

MAR 28 1969

Their E.E. 1969 N.S. Classroom Model of an Information and Computing System

by

#### MICHAEL DAVID SCHROEDER

Submitted to the Department of Electrical Engineering on January 20, 1969 in partial fulfillment of the requirements for the Degree of Master of Science.

#### ABSTRACT

This thesis describes the Classroom Information and Computing Service (Clics), a pedagogical computer based information system to be used as a case study in the subject "Information Systems" in the Department of Electrical Engineering at M. I. T. Clics is an abstraction of the Multiplexed Information and Computing Service (Multics) that is currently being implemented by Project MAC at M. I. T. in cooperation with Bell Telephone Laboratories and the General Electric Company. As such, it is an example of a computer utility, currently the most general type of computer based information system that is available. Clics is derived from Multics by a combination of simplifying the mechanisms of Multics and removing some of its more exotic features, and embodies research into ways to simplify the mechanisms of Multics without sacrificing service objectives.

The thesis contains the specification notebook for Clics that will be used in class in the Spring, 1969 presentation of "Information Systems". This notebook specifies both the hardware and control programs of the model system in sufficient detail for students to develop a structural as well as functional understanding of its operation and mechanisms. Projects are suggested which require alteration to the system to increase its efficiency and/or capabilities and allow the students to trace the implications of small changes in a complex system. As the primary case study for the subject, Clics will provide specific examples of the mechanisms and complexities in a general purpose information system.

Thesis supervisor: Jerome H. Saltzer

Title: Assistant Professor of Electrical Engineering

#### ACKNOWLEDGEMENTS

Because this thesis is based primarily on a developing system which is not yet fully documented the main source of information has been personal conversations with the people involved in the development effort. I wish to acknowledge the contributions of J. H. Saltzer, R. M. Graham, E. I. Organick, and D. D. Clark in this respect. Work reported herein was supported in part by Project MAC, and M. I. T. research program sponsored by the Advanced Research Projects Agency, Department of Defense, under Office of Naval Research Contract Number Nonr-4102(01). Reproduction in whole or in part is permitted for any purpose of the United States Government.

## TABLE OF CONTENTS

| Foreword                                      | 5   |

|-----------------------------------------------|-----|

|                                               |     |

|                                               |     |

| Part I:                                       |     |

|                                               |     |

| Introduction                                  | 6   |

| Service objectives of a computer utility      | 11  |

| Derivation of Clics from Multics              | 15  |

| Use of Clics in 6.233                         | 22  |

| The specification notebook                    | 24  |

| Conclusion                                    | 26  |

|                                               |     |

| Part II:                                      |     |

| The 6.233 Clics System Specification Notebook | 29  |

| References                                    | 215 |

#### FOREWORD

This thesis presents the <u>Classroom Information</u> and <u>Computing</u>

<u>Service</u> (Clics), a model computer utility which will be used as a case study for a subject in the undergraduate computer science curriculum within the Department of Electrical Engineering at M. I. T.

The thesis is divided into two parts. The first part, containing six sections, describes the context for Clics, and discusses such things as its background, development, and use. The second part is the specification notebook for the system that will be used in the classroom to present the model to students.

#### PART I

### Introduction

The <u>Classroom Information</u> and <u>Computing Service</u> (Clics) that is described by this thesis is a model of a computer utility that is to be used as a case study in the classroom. As a first step in defining more precisely what Clics is, the undergraduate subject in which it is to be used is described.

At M. I. T. an elective three subject sequence is being developed in computer science within the Department of Electrical Engineering. The subjects are "Programming Linguistics" which considers linguistic constructs for specification of algorithms, "Computational Structures" which discusses hardware and software means of implementing these, and "Information Systems" which considers complexity in information systems. It is for the third subject in this sequence, designated 6.233, that the Clics system is to serve as a case study.

The description of 6.233 in the Institute's general catalog [1] lists the specific topics covered by the subject and is thus a good indicator of its scope. Also mentioned is the role of a model information system, the role to be filled by Clics. The catalog description reads:

Sources of complexity in information systems, with particular emphasis on problems arising when a single information system serves a community of users. Contrast of problems intrinsic to purposes of use with those related to technical limitations.

Study of specific design objectives such as reliability, maintainability, information storage, controlled information sharing, ability to withstand change, and ease of administration. Effect of these and other design objectives on system implementation demonstrated in a model system. Comparison and contrast of model system with current state-of-the-art systems, including both general purpose community computing facilities and information systems dedicated to a special task such as telephone line switching or air traffic control.

The term "information system" is intended to include any system which stores and processes information. Thus a library, a telephone system, and a computer system are all valid examples. The purpose of the subject is to describe some of the complexities of interaction that appear when a group of individually understood components are put together to form an information system, and to indicate some of the techniques for dealing with these complexities. The desired result is to prepare students to evaluate information systems with which they may come into contact, and to prepare them to assist in the design of new information systems should the opportunity arise.

A brief outline of the approach used in 6.233 [2] further clarifies the role of Clics. The subject begins by considering information systems in a general way, using the examples of a library, an airline ticket reservation system, and a community computer facility. From each of these examples is developed a list of objectives with the apparent intent of describing ways to derive the systems from the objectives. It is then pointed out that, while systematic approaches to synthesizing a system from its objectives are beginning to appear, a general technique for doing so does not exist. At this point the Clics

system is introduced and the specification notebook made available, and the subject split into two streams. One continues the conceptual approach already begun while the other considers the model system, attempting to construct the connections from Clics to the set of objectives that appeared to be desirable in an information system from the previous examples. The second stream actually constitutes a laboratory for the subject. Homework problems based on the model are assigned and each student is given several projects involving modification of the model system.

The case study technique is a useful vehicle in 6.233 because, as in any subject where a formal theory is not available, the ideas here are elusive, difficult to formulate, and difficut for students to grasp. Providing a specific example in which students can observe a set of mechanisms based on the ideas presented incorporates into the subject a piece of solid ground. At the same time, however, the obvious danger that the students will interpret the purpose of the subject to be the presentation of the mechanisms of the model system is present. Because the model provides relatively solid ground, they will tend to grasp it too firmly. The solution to this problem lies entirely in proper emphasis.

That the model system chosen for the case study in a subject on information systems is a computer utility results from the fact that computer utilities are the most general kind of information systems presently available and they contain many clear examples of mechanisms directly related to specific objectives.

There are several precedents for using a case study when teaching subjects related to complex systems. One successful model is the Classroom Assembly Program (CAP) developed by Corbató, Poduska, and Saltzer [3]. It presents an easily understood mechanism for performing the basic operations of typical computer language translator programs, and has been used in several computer programming subjects. Graham's Instructional Translator (Instran) [4] approaches the complexities of compiler programs in the same manner, and has also been used in class work. The SAMOS computer developed by the School Mathematics Study Group at Stanford University [5] allows students to become familiar with the capabilities of a typical computer as a step in teaching them the art of programming. This computer model has been simulated on several machines, and students allowed to construct and run programs on it. Sherman has described a model of a batch type operating system [6] (both hardware and control programs) for the same purpose, to teach programming. Unfortunately, none of these are applicable to 6.233, for each is an example of a very restricted class of information systems. Extending the technique and constructing a model of a computer utility, however, is an obvious approach to the topics of 6.233.

Up to this point we have considered the subject in which Clics is to function as a case study, and have described the role of the model system in the material to be presented. We now turn to the model system itself and consider briefly the scope and basis of Clics. Clics is a model of a computer utility. It is a system providing computational ability and information

storage to a community of users in much the same way that the telephone system provides communication ability to a community. It is easily accessible and general in scope. The specific background for Clics is found in the Computer Systems Research Group in Project MAC at M. I. T. which has for several years been engaged in the development of large time-shared computer systems. The first product of this effort, the Compatible Time Sharing System (CTSS) which runs on a modified IBM 7094 [7] has been usefully in operation for several years. Currently a more powerful system, the Multiplexed Information and Computing Service (Multics) which runs on a General Electric 645 computer system [8-16], is being developed and implemented in conjunction with Bell Telephone Laboratories and the General Electric Company. Clics is based on Multics. Multics is chosen as a basis because it is the only system in existence which provides an indepth implementation of a computer utility in an understandable form.

Clics is a model in the sense that it is an abstraction of the Multics system. It is also an extension of Multics, for it embodies research into finding ways to simplify the mechanisms of Multics without sacrificing the service objectives. Clics is a system in its own right, as well, for it is implementable, and would be useful if it were implemented.

Two basic types of abstraction are used to obtain Clics from Multics. As suggested above, simplification of mechanism is the most important. The second is the removal of some of the more exotic features of Multics. In addition, certain areas of Multics to be

included in Clics which have not yet been abstracted in detail are temporarily bridged over with overviews. These bridges, which will be replaced later with detailed mechanisms, provide the model with a completeness that allows it to be used in the classroom while development continues in these areas. Each technique will be discussed in more detail later, and specific examples will be given.

In the five remaining sections of Part I we describe a set of service objectives which characterize a computer utility, describe in more detail the derivation of Clics from Multics, discuss the use of Clics in the classroom, describe the specification notebook that constitutes Part II, and offer some observations and conclusions.

## Service objectives of a computer utility

The objectives that result from consideration of various examples of information systems in the first part of 6.233 define more precisely the scope of a computer utility like Multics and Clics, for these objectives describe an information system in its full generality, and a computer utility is intended to be the most general possible computer system. In particular, they specify the kind of service that a computer utility must provide. To more carefully define the notion of a computer utility, then, and specifically to document the service that Clics is intended to provide (and illustrate to the students), we list these objectives and briefly expand each as it applies to a computer utility.

- 1. information storage

- 2. multiple users

- 3. controlled information sharing

- 4. simultaneous processing of real time imputs

- 5. specified real time response

- 6. scheduled availability

- 7. user self protection

- 8. ability to expand

- 9. ability to adapt to change

- 10. performance measurement

- 11. resource management

Following is a paragraph expanding each objective briefly.

- 1. Information storage is a primary objective of a computer utility. Such a system is of little value to a user if he must always approach it with the entire body of information to be considered in hand. The system must allow each user to build up over a period of many uses a history of information that can be easily accessed. The ability to apply to this information a content related organization must be present. Because the utility serves as the primary storage medium for much of the information, the storage must be reliable.

- 2. A computer utility is a single system serving a community of users. An obvious parallel is the telephone system. The benefits derived there through the use of a single system for many users apply here as well. First of all, each user has available a range and depth of services (some of which are only occasionally used by him) that he could not support if they were all dedicated to his use. Secondly, it allows easy communication between members of the user community. Such would not be possible, for instance, if each had

instead his own small computer, for the situation would be similar to that which would exist if there were several uninterconnected telephone systems.

- 3. The communication between users that occurs in the environment of a computer utility takes the form of sharing information. users are to benefit from each other's work to the fullest extent possible the computer utility must allow each user to share in a controlled manner his body of stored information. The same kind of sharing occurs when users execute service programs provided by the computer utility, such as compilers and library routines. Control is important, for many users need to maintain private information. Company payrolls, budget reports, and grade sheets are examples of private information. These users will make full use of the system only if this information will remain private when stored within it. Required is the ability to define exactly who may use each logical unit of information and in what manner. (The means to allow information to be read, but not altered, for example, is very useful.) The same control may be applied to limit access to the system's control programs.

- 4. Because many users depend upon a single system, apparent simultaneous processing of real time inputs is required. It must be possible for a reasonable percentage of the total community to use the system simultaneously. Thus, requests of and responses from the computer utility need not be coordinated by the users.

- 5. If the time required to obtain a specified response from the computer utility varies widely it will discourage system use

and thus reduce the effectiveness of the system. An additional benefit is derived if this response time is small enough to allow interactive use.

- 6. A computer utility must also be available on a prescheduled basis for much the same reason. The ideal schedule from the point of view of the users is 24 hours each day. Careful integration of system maintenance into the operation of the system can make this goal realizable.

- 7. The objective of user self protection recognizes that users make errors that can inflict self damage. The computer utility must minimize such damage.

- 8. The user community of a computer utility will tend to grow larger if the system is functioning properly, and the per user demand on the system will increase. Continued service under these circumstances requires that the ability to expand gracefully be an objective. Faced with the prospect of a system becoming overloaded in the predictable future, users will take their work elsewhere, if possible.

- 9. For the same reasons the ability to adapt to change must also be included in the list of objectives. This includes both changes in the quality of the user community demand (the need for a new compiler, for example) and advances in technology. It must be possible to incorporate new or improved hardware and control programs into the system with minimum disruption of service.

- 10. Enough meters must be built into the system so that proper account may be made of system resources. Only by measuring usage carefully can the need to expand be determined and can users be charged for

the resources that they consume. Such measurements also allow the system to be tuned to give highest performance.

11. Objectives 2 and 4 together imply that decisions must be made between users competing for system resources. Optimum system performance demands careful management of these resources.

The objectives taken together define a system with general computing and information storage ability that is well behaved and convenient to use. Making computers available in this form is certainly a step toward their general use and acceptance. It should be emphasized that, while the concept of a computer utility is absolute, the specific set of objectives presented is not unique. There are other cuts of the ideas that produce a different set describing the same phenomena.

### Derivation of Clics from Multics

We now return to discuss in more detail the derivation of Clics from Multics. Fundamentally Clics is an abstraction of the Multics system, and uses the same methods to meet the same general service objectives. Multics, however, is very large and very complex, and many simplifications are made to produce a model that is (hopefully) digestable by students in the time of a semester. The two methods of abstraction that are used (as mentioned in the Introduction) are simplification of mechanisms, and removal of some of the more exotic features. Following, each is considered more carefully and specific examples are provided.

The first is the most interesting, for it embodies basic research into ways to accomplish the goals of Multics with simpler mechanisms

than used by Multics. A good example is found in the mechanisms used by each to provide information storage. Multics uses a multilevel memory system incorporating core, drum, and disk storage devices. Fixed sized blocks of users' programs are paged from the drum to core on demand, replacing the removable blocks in core which have gone the longest without being referenced. The replaced blocks move from core to the drum. The same sort of paging occurs between the drum and the disk (via core), though less often. All paging is transparent to the user programs, which always reference their address spaces with a two dimensional address composed of a segment number and a word number. It is not transparent to the system control programs, however, and in fact enormously complicates them. Below a certain level the control programs have the responsibility of keeping track of the location on the storage devices of each block of information, initiating the transfer of blocks between devices, and updating the tables which allow the hardware to translate the two dimensional addresses presented by user programs into absolute core addresses. The contents of the address translation tables change, of course, each time information moves from one place to another. In effect, the control programs have the responsibility of making the multilevel memory system appear as a single level system. The hardware assistance in this matter is confined to performing the address translation from two dimensions to an absolute core address using an in-core segment map associated with each user program and an in-core page map associated with each segment, and to generating faults when a two dimensional address specifies information not in

core. This design, of course, was constrained by the available hardware.

In Clics the control programs are greatly simplified by moving as much as possible of the Multics mechanism described above into the hardware. The Clics hardware memory system consists of identical memory modules, each containing words that are individually addressable. These modules provide the entire memory of the system. The memory is seen by the processors and input/output controllers as having a single level, for all words can be accessed with a single sequence of binary addresses. The control programs are relieved of the burden of making a multilevel memory appear as having only one level. It is never necessary for the control programs to initiate the transfer of blocks of information from one device to another or perform the attendant bookkeeping, as in Multics. Memory is still viewed as containing fixed sized blocks of information, but this is for organizational purposes only. Aside from the lowest levels of the storage management subsystem which construct segments from memory blocks by linking them together with page maps, the control programs use two dimensional addresses almost exclusively, just like the user programs. The most important aspect of this scheme may be summarized by saying that each word of information in the entire Clics system has a unique apparent address that does not change. As can be predicted, the result is that the control programs of Clics are much simpler than the corresponding programs in Multics, especially those concerned with storage management.

The specification notebook for Clics does not describe in detail the mechanisms within each memory module, but such memory modules are currently technologically possible. One approach to their construction would be to include in each several layers of progressively slower but higher capacity storage devices, and use automatic hardware paging. (Automatic hardware paging used in the IBM 360/85 system [17].) Thus information currently being referenced would reside in the smallest and fastest memory device while information not being referenced would automatically move to slower and larger devices. Each such memory module could contain many million words of storage, and would preserve the unique correspondence of address and data word when viewed from the outside. A specific address would always retrieve the same information, regardless of on which storage device within a memory module it happened to reside at the time of reference.

Before leaving this example a practical result of the research that went into describing this aspect of the Clics system should be noted. Partly because of the great reduction in complexity achieved in the control programs of Clics with this scheme, the control programs of Multics are currently being re-evaluated to find ways to further isolate the mechanisms controlling paging so that the remaining control programs may view memory as one level.

There are many other examples of simplification of mechanisms

in Multics to obtain the corresponding mechanisms in Clics. Below are listed a few more. In each case the Clics mechanism is described first, followed by the corresponding Multics mechanism in parentheses.

- . Rings of protection as described in Graham's paper [18] are implemented in Clics by including in each Clics processor a ring register which is compared on each reference to memory with the protection information associated with the referenced segment.

(Because the GE-645 processor lacks a ring register, Multics implements rings of protection by maintaining a separate definition of a program's address space for each ring that it occupies.)

- . The Clics system uses a 64-bit word length which allows full two dimensional addresses to be contained in a single word.

(The 36-bit word length of the GE-645 system forces the use of word pairs in Multics to contain two dimensional addresses and other complex addressing conventions.)

- . The interrupt hardware of the Clics system embodies only one level of interrupt and allows processors to accept interrupts only between the execution of instructions. (The Multics interrupt hardware has multiple levels of interrupts and allows processors to accept interrupts at several points during the execution of an instruction.)

- . The instruction set of a Clics processor is designed so that any instruction causing a fault can be re-executed from the beginning after the fault is repaired. (The GE-645 processor instruction set requires that faulting instructions be restarted at the

point of the fault. This requires that more complete processor state information be saved at the time of the fault than in Clics.)

- . In the Clics processors index and pointer registers are functionally combined into a single set of general purpose registers.

(Both index and pointer registers appear in a GE-645 processor.)

- . The instruction set of each Clics processor includes a special CALL instruction which saves all machine conditions, performs any necessary procedure stack switching, and automatically changes the ring in which the processor is running when necessary. (Multics uses a several instruction calling sequence, and uses faults generated by calls across ring boundaries to interpose into the call a procedure that switches stacks and redefines the address space to correspond to the new ring.)

All of these features of the Clics hardware make possible significant reductions in the complexity of the Clics control programs, as compared to the corresponding Multics control programs.

We now move to an example of the second method of abstraction, the removal of certain of the more exotic features of Multics.

Multics has a rather complete user control facility that performs the complex task of balancing the load of the system against the available processor and core resources. This facility also allows for absentee user programs to be scheduled and then be automatically run by the system when the proper time arrives. The Clics system does not include such a facility. It is left out because other portions of the system contain sufficient examples for 6.233, and it is not an integral part of the basic mechanisms of the system.

In other words, the system is complete without it. Load control is a self-contained package that can be added later, if necessary, without restructuring the currently defined Clics system. It may also serve as the source of some good student projects. In general, facilities of Multics are ignored in the model only when they are peripheral to the basic system and when exclusion will not destroy the completeness of the model.

As mentioned in the Introduction, certain areas of Multics to be included in Clics that have not yet been abstracted in detail are temporarily described with general overviews. The overviews provide the model with a completeness that allows it to be used in the classroom while development continues in these areas. Two examples in the version of the notebook presented in this thesis are the areas of system initialization and input/output. Certainly the model system cannot be considered complete unless it includes both. Presently input/output is bridged by an overview of the specialized input/output processors of the hardware system, and another overview which functionally describes an input/output subsystem which only allows a program to read and write a permanently attached typewriter terminal. The details of system initialization are not described yet, either. What is provided is an overview of the system's condition immediately after initialization has occured.

In this section we have seen examples of the methods of abstraction used to derive Clics from Multics. They result in a system meeting substantially the same service objectives as Multics, but which exhibits simpler mechanisms. The specific contents of

the Clics system can be determined from the specification notebook presented as Part II of this thesis.

### Use of Clics in 6.233

This section defines more precisely the role of the Clics system in 6.233. It is difficult to specify exactly how the case study will be used, for the subject is still being developed and the specification notebook has not yet been used in the classroom. (Its first use will come in the Spring semester for the 1968-69 school year.) Three uses are seen at this time: students will study Clics as an example of a computer utility meeting the objectives developed for information systems, homework problems will be based on the system, and student projects will be based on it.

The model will be introduced by making reading assignments in the specification notebook and spending one out of the four class hours each week in a laboratory discussing the material read. The emphasis of these discussions will be on how the mechanisms of the model work, why they are necessary, and what alternate mechanisms would work in their places. As the students become conversent with a portion of the model system, homework problems will be assigned that are based on that material. These problems will examine the operation of mechanisms of Clics in given circumstances and will force students to consider the effects of small changes in these mechanisms. Students will also be assigned projects based on the model that require them to make certain modifications or additions to the system with the aim of increasing its efficiency or extending its capabilities. Successful completion of these projects will require

a good understanding of the Clics system and careful consideration of the implications of the changes on all system parts. For example, certain table lookups within the system are implemented with simple linear search methods. One project is to replace the lookup mechanisms with a more sophisticated version employing hash coding. A more difficult project is to propose an implementation for an associative memory in the processors to speed the translation of two dimensional addresses to absolute memory addresses. The specification notebook describes some other projects based on the mechanisms described in detail in this version of the notebook. This list, however, is by no means fully developed. More will certainly be added later.

One section of the specification notebook for Clics describes the Clics Implementation Language (CIMPL), a high level PL/I-like language in which the control programs of Clics are to be written. CIMPL was developed for 6.233 by Professors Graham and Saltzer, and D. D. Clark. (The language specification is not included in the specification notebook contained in this thesis, but will be included in that given to students next spring.) Part of learning about Clics will include learning to specify algorithms in CIMPL. Thus both homework sets and student projects can include programming, if appropriate. The study of CIMPL is an integral part of the case study of Clics, because the language contains constructs that are particularly suited to expressing the class of algorithms that appear in control programs for computer systems. Examples of such constructs are data structures, pointer variables, and procedures

that are automatically recursive.

As a rough estimate of the weight to be given Clics in 6.233 it is expected that consideration of this case study, both in and out of the clasroom, will occupy one quarter to one third of the time devoted to the subject by each student. This includes time spent doing related homework sets and completing projects.

## The specification notebook

Part II of this thesis contains the specification notebook for the Clics system. The method of description chosen is the same as that used to document Multics. The highly modular specification notebook contains a section for each piece of hardware, each procedure and data base, plus assorted overviews and discussions of system aspects that cut across hardware module, procedure, or data base boundaries. The Clics notebook is written at approximately the same level of detail as that for Multics, but is significantly shorter.

The notebook that is presented with this thesis is a preliminary version. It appears as it will be used in the spring, 1969 presentation of 6.233 (minus the CIMPL language specification) but does not contain all sections that are planned to be included eventually. The dated items appearing in the notebook's table of contents are completed and included in the preliminary version. The remaining items listed there reflect work to be done on the model in the immediate future. The table of contents taken as a whole, however, does not reflect the ultimate specification notebook

exactly, for work in some areas has not progressed to the point where the section titles have been specified. In connection with the bridging over described earlier, note that overviews are provided for most unfinished areas so that students have the flavor of the missing sections. In most cases these overviews will be replaced by more detailed overviews when the mechanisms are specified more carefully.

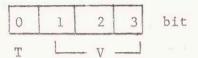

The CIMPL language is used in two ways in the specification notebook: to declare data bases and to define entry points. A brief description of certain characteristics of the CIMPL language will allow these declarations and definitions to be understood in the absence of the CIMPL manual. The data base declarations may be read as PL/I based structures. The only data types are integer, character, bit, and pointer. Integers and pointers occupy a single word. A variable of type bit occupies one binary bit. A variable of type character occupies eight binary bits. Bit and character strings are not allowed, but one dimensional arrays of all data types are allowed. Consecutive bit and character variables in a structure declaration are packed left to right into consecutive bits of a storage word. The declaration for an entry point specifies the entry name as a label, and declares the number and type of arguments in the bound variable list in parentheses. For notational convenience input arguments are named with lower case letters while output arguments are named with upper case.

#### Conclusion

As a conclusion to Part I the significance of the work reported in this thesis is summarized and the future development of the Clics system is outline. The basic significance of Clics is that it allows the presentation to students of material which up to now has been inaccessible to them. It has been the case that for a student to acquire the ability to evaluate and innovate information systems, particularly computer based information systems, he had to become involved in the design, construction, or maintenance of such systems and slowly build a background of experience from scratch. All too frequently this method resulted in exposure to a restricted class of information systems. Such background was not available in a generalized, condensed form. With primary support from the Clics system, 6.233 will provide an alternate background so that students need not start from scratch in gaining experience. other words, the model system will allow something to be taught that was not being taught up to now.

A secondary significance of Clics is that it demonstrates the large simplifications of mechanism that are possible in a system like Multics when hardware and control programs can be specifically designed to meet the objectives of the system, and when simplicity of mechanism is viewed as an important objective in its own right.

The claim is not made that Clics is the only model useful in 6.233, or that Clics embodies the only way to meet the service objectives stated as desireable in a computer utility. Although Clics

is the primary case study, other examples of information systems are considered in 6.233 (the Electronic Switching System developed by Bell Telephone Labroatories [19], for example). As stated earlier, a model of a computer utility is chosen because computer utilities are the most general type of information system currently available, and the means used in Clics to meet the service objectives are abstracted from Multics because Multics is the only currently available system providing an in-depth implementation of them.

It should also be emphasized that this thesis presents a snap-shot of work in progress. The argument that the snapshot is complete enough to be of interest follows from the use of this preliminary version of the notebook in the classroom next semester and the existence of overviews bridging unfinished areas.

The immediate future of Clics includes, of course, its use in 6.233 this spring and the completion of the specification notebook sections specifying in detail the areas bridged over with overviews. As a result of its use in the classroom a comprehensive list of student projects will be defined and debugged. It is also expected that the model itself will be debugged by its exposure to students, and that ways will be found to rewrite specific pieces of the specification notebook to make them clearer.

A concurrent activity will be the production of listings in the CIMPL language for all the control programs of Clics. This has already begun - two undergraduate students are writing the procedures of the storage management subsystem. These listings will be included in the specification notebook as part of the system descrip-

tion. They will be valuable both in allowing students to develop a very detailed understanding of the mechanisms in Clics and in demonstrating the use of a high level language as a means of coping with the complexity of a computer utility.

A compiler is being constructed for the CIMPL language. At the present time it is planned that it will only check the syntax of programs, but thought is being given to constructing some sort of simulator in which the control programs of Clics, written in CIMPL, can be run. This will allow students to actually make changes to the system, run the altered system, and observe the result of their work.

### PART II

## The 6.233 Clics System Specification Notebook

The following pages present the preliminary version of the specification notebook for the Clics system. It begins with a table of contents listing the sections of the notebook.

## 6.233 Clics System Specification Notebook

Table of contents

Date: **MAN 1 3 1969**

## A. Introduction

O. System overview

1. Student projects 12/16/68

2. Notebook organization

## B. CIMPL programming language manual

# C. Hardware

| 0. | Organization OO. Overview of hardware organization | 12/16/68  |

|----|----------------------------------------------------|-----------|

|    | Ol. Major module interface                         | 12/16/68  |

|    | 02. Control communication                          | 12/16/68  |

|    | 03. Tape device interface                          | 12/16/68  |

|    | 04. Typewriter device interface                    | 12/16/68  |

|    | 05. Hardware configuration                         | 12/16/68  |

|    | os. hardware configuration                         | 12/10/00  |

| 1. | Processors                                         |           |

|    | 00. Overview of processor capabilities             | 12/16/68  |

|    | Ol. Processor dependent storage formats            | 12/16/68  |

|    | 02. Program addressible registers                  | 12/16/68  |

|    | 03. Operand specification interpretation           | 12/16/68  |

|    | 04. Address mapping                                | 12/16/68  |

|    | 05. Segment access protection                      | 12/16/68  |

|    | 06. Processor instruction set                      | 12/16/68  |

|    | 07. Symbolic instruction representation            | 12/16/68  |

|    | 08. Processor logic overview                       | 12/16/68  |

|    | 09. Hidden processor registers                     | 12/16/68  |

|    | 10. Instruction cycle logic                        | 12/16/68  |

|    | 11. Fault/interrupt mechanism of instruction cycle | 12/16/68  |

|    | 12. Address mapping logic                          | 12/16/68  |

|    | 13. Access checking logic                          | 12/16/68  |

|    | 14. Directory of processor abbreviations           | 12/16/68  |

| •  |                                                    |           |

| 2. | Input/output controllers                           | 10/10/100 |

|    | 00. Input/output controller overview               | 12/16/68  |

|    | 01. Input/output controller mailbox segment        | 12/16/68  |

|    | 02. Input/output controller control words          | 12/16/68  |

| 3. | Memory modules                                     |           |

|    | 00. Overview of memory module organization         | 12/16/68  |

|    | Ol. System controller                              | 12/16/68  |

|    | 02. Storage unit                                   | 12/16/68  |

|    | 03. Clock driver unit                              | 12/16/68  |

|    |                                                    |           |

| С. | 4  | Tape handlers                                  |                      |

|----|----|------------------------------------------------|----------------------|

| •  |    | 00. Overview of tape handlers                  | 12/16/68             |

|    |    |                                                |                      |

|    | 5. | Typewriter terminals                           |                      |

|    |    | 00. Overview of typewriter terminals           | 12/16/68             |

|    |    |                                                |                      |

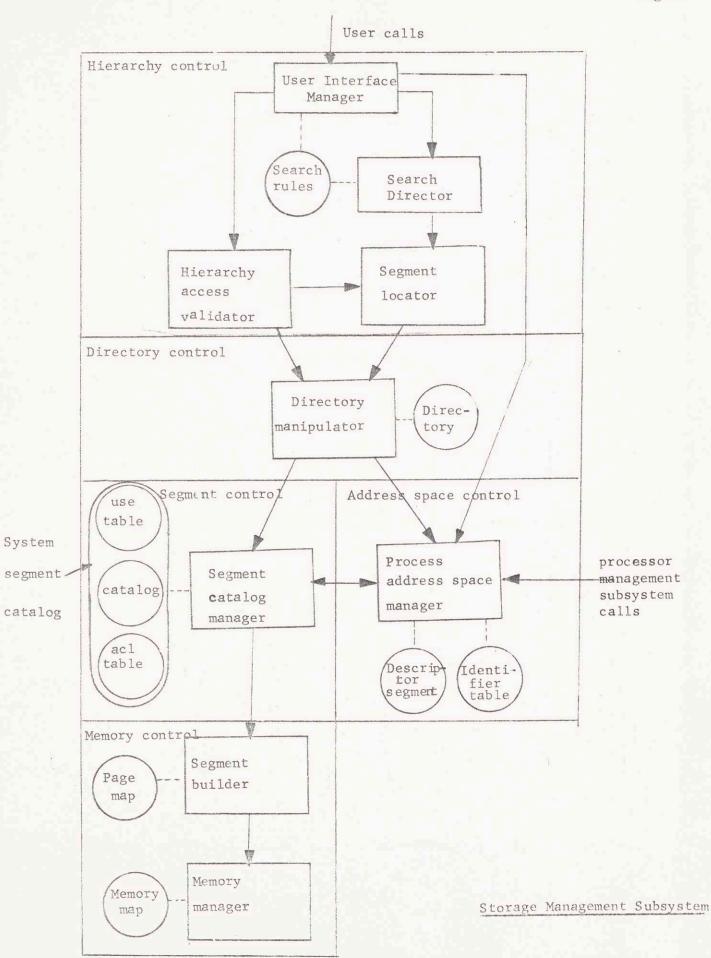

| n  | C+ | orage management subsystem                     |                      |

| υ. | 50 | orage management subsystem                     |                      |

|    | 0. | General                                        |                      |

|    |    | 00. Storage management subsystem overview      | 12/16/68             |

|    |    | Ol. Sharing and protection of segments         | 12/16/68             |

|    |    | 02. Hierarchy organization                     | 12/16/68             |

|    |    |                                                |                      |

|    | 1. | Memory control                                 | N av a voice havaner |

|    |    | 00. Memory map                                 | 12/16/68             |

|    |    | 01. Memory manager                             | 12/16/68             |

|    |    | 02. Segment structure                          | 12/16/68             |

|    |    | 03. Segment builder                            | 12/16/68             |

|    | 0  | 0 - 1                                          |                      |

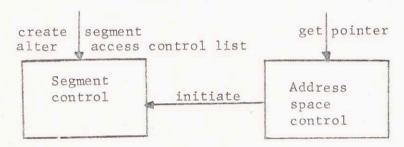

|    | 2. | Segment control                                | 12/16/60             |

|    |    | 00. System segment catalog                     | 12/16/68<br>12/16/68 |

|    |    | Ol. Segment catalog manager                    | 12/10/00             |

|    | 3. | Address space control                          |                      |

|    |    | 00. Descriptor segment                         | 12/16/68             |

|    |    | Ol. Identifier table                           | 12/16/68             |

|    |    | 02. Process address space manager              | 12/16/68             |

|    |    |                                                |                      |

|    | 4. | Directory control                              |                      |

|    |    | 00. Directory segment                          | 12/16/68             |

|    |    | Ol. Directory manipulator                      | 12/16/68             |

|    | 5  | Hi awayahu a antwal                            |                      |

|    | ٥. | Hierarchy control  OO. Segment locator         | 12/16/68             |

|    |    | 01. Hierarchy access validator                 | 12/16/68             |

|    |    | 02. Search rules                               | 12/16/68             |

|    |    | 03. Search director                            | 12/16/68             |

|    |    | 04. User interface manager                     | 12/16/68             |

|    |    | of, ober menager                               | 12/10/00             |

|    |    |                                                |                      |

| E. | Pr | ocessor management subsystem                   |                      |

|    | 0  |                                                |                      |

|    | 0. | General                                        | 10/16/60             |

|    |    | 00. Overview of processor management subsystem | 12/16/68             |

|    |    | Ol. Process table                              |                      |

|    | 1  | Traffic control                                |                      |

|    | т. | 00. Overview of traffic control                |                      |

|    |    | Ol. Ready list within process table            |                      |

|    |    | 02. Process exchanger                          |                      |

|    |    |                                                |                      |

12/16/69

| Ε.      | 2. Fault/interrupt con | trol                 |          |

|---------|------------------------|----------------------|----------|

|         |                        | lt/interrupt control |          |

|         | Ol. Fault/interrupt    | interceptor          |          |

|         | 02. Fault handler      |                      |          |

|         | 03. Interrupt sende    | r                    |          |

|         |                        |                      |          |

|         | 3. Process control     |                      |          |

|         | 00. Overview of pro-   | cess control         |          |

|         | Ol. Login              |                      |          |

|         | 02. Logout             |                      |          |

|         | 03. Housekeeper        |                      |          |

|         | 04. Listener caller    |                      |          |

|         |                        |                      |          |

|         |                        |                      |          |

| F.      | Command subsystem      |                      |          |

|         |                        | a range              | 12/16/68 |

|         | O. Overview of command | subsystem            | 12/10/00 |

|         |                        |                      |          |

|         | 1. Listener            |                      |          |

| . 5     | 2 Ch - 11              |                      |          |

|         | 2. Shell               |                      |          |

|         |                        |                      |          |

| C       | Operations subsystem   |                      |          |

| G.      | operations subsystem   |                      |          |

|         | 0. System loading and  | initialization       | 1/13/69  |

|         | 0. 2,000               |                      | ,,       |

|         | 1. Hardware configurat | ion table            |          |

|         |                        |                      |          |

|         |                        |                      |          |

| Н.      | Input/output subsystem |                      |          |

|         |                        |                      |          |

|         | 0. Overview of input/o | utput subsystem      | 1/13/69  |

|         |                        |                      |          |

|         | 1. I/O controller data | process              |          |

|         |                        |                      |          |

|         | 2. Typewriter read/wri | te                   |          |

|         |                        |                      |          |

|         | 3. Status receiver     |                      |          |

|         |                        |                      |          |

|         | 4. Channel assignment  | table                |          |

|         |                        |                      |          |

| 12-11 C |                        |                      |          |

| I.      | Communication conventi | ons                  |          |

|         |                        | 14.1                 |          |

|         | O. Procedure and data  |                      | . / /    |

|         | 00. Overview of dyn    | amic linking         | 1/13/69  |

1. Call - entry - save - return and procedure stacks

Ol. Linker

02. Linkage segment

# 6.233 Clics System Specification Notebook

Table of contents Page 4

I. 2. Entry vectors

1/13/69

3. Locker

1/13/69

4. Character set

# J. Clock subsystem

- O. Overview of the clock subsystem

- 1. Clock reader

## K. Command library

O. Command construction standards

6.233 Clics System Specification Notebook

Section A.1

Date: DEC 16 1968

### Identification

Student projects

### Purpose

This notebook section presents possible student projects based upon the Clics system, as it is described in the remaining notebook sections. The projects range from easy to difficult, and by no means exhaust the possibilities. It is expected that students will also be able to suggest projects which interest them. In each case the project is a change or addition to the system that involves altering the hardware or software. Projects are to be written-up as new or changed notebook sections, with flow-charts and/or listings when applicable.

A preliminary report in which the student presents his understanding of the issues involved and problems to be solved, and outlines his solutions will aid in determining if he has a good grip on the problem, and allow exchange of ideas between instructor and student.

The project list in this version of the Clics notebook is not fully developed. A few projects are completely described to provide the flavor of suitable project statements. Others are only identified in a list, or have not been thought of at all.

Appendix

## Project 1: Access mode indicator execute permit bit

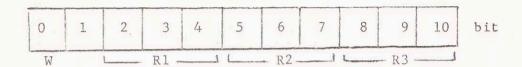

This project is to add an execute permit bit (E) to the format of the access mode indicator that appears in each segment descriptor word, and to modify the processor logic to check this bit each time an attempt is made to execute a word of a segment as a machine instruction.  $E=1\ \&\ R2\ge procedure$  ring register of a processor must be true before the processor will retrieve an instruction to be executed from a segment. If it is not true then an illegal procedure fault should be generated.

The suggested implementation is to add an EXECUTE operation indicator to those recognized by the address mapping logic of a processor, and to have the instruction fetching logic retrieve the instruction to be performed with it. The address mapping logic will return the instruction word only if the supplied procedure ring register value properly compares to the R2 ring number in the access mode indicator of the containing segment, and if the contained E bit is "on".

Also included in the project is making the alterations to the procedures and data bases of the storage management subsystem that will allow the E bit to be used. These changes, though minor in each case, are surprisingly numerous.

Section A.1 Appendix

# Project 2: Address mapping logic associative memory

This project is to add an associative memory to the address mapping logic of the processors that will make it unnecessary to retrieve segment descriptor words (SDWs) repeatedly with repeated reference to the same segment by the processor. This project is not easy, and there are several difficult problems lurking just below the surface.

The general implementation scheme suggested is to define a set of live registers (how many?) that can be quickly searched by the basic address formation logic of the address mapping logic for the currently needed SDW. The intent is that these registers contain the SDWs of the segments most recently referenced by the processor. The search is ordered, with the most recently used SDW being inspected first. Only if this search is unsuccessful is the SDW retrieved from memory. A SDW retrieved from memory replaces the SDW in the associative memory that has gone longest without use, and becomes the most recently used.

Some mechanism must be described for clearing the associative memory. One obvious occasion when this is necessary is when a processor is switched to the address space of another process by changing the contents of the descriptor base register. The same segment numbers may correspond to different SDWs in the new process. This case can be handled reasonable easily, for the simulus for clearing the associative memory comes from within the processor, whose associative memory is to be cleared.

Other cases may be less obvious, and more difficult to handle. For example, each time the fault bit in an SDW of some process (A) is set "on" by the process address space manager of the storage management subsystem executing in another process (B), and process A is concurrently running on a processor, that processors' associative memory must be cleared. This means that the processor on which process B is executing when the fault bit is set "on" must signal the processor on which process A is executing to clear its associative memory.

One solution to these problems may be a machine instruction which clears a processors' associative memory. This could be used immediately after each load descriptor base register instruction, and could also appear as the first instruction of the fault/interrupt interceptor. Thus, the sending of an interrupt to a processor would cause it to clear its associative memory. The ability of a processor to ignore interrupts (run with the interrupt inhibit switch set "on") may cause some problems, however.

Another solution may be to have each processor clear its associative memory automatically as part of the load descriptor base register instruction, and to clear it at the beginning of an instruction cycle if any interrupt present line to the processor has a signal on it, whether interrupts are inhibited or not.

### Project 3: Improved memory map and memory manager

This project is to design a new memory map and memory manager (both part of the storage management subsystem) that will not require all empty blocks of memory to be linked together at system initialization time, and that will allow more than one process at a time to assign or release memory blocks. The interface presented by the new memory manager should match exactly that currently described. A suggested implementation is to divide the memory map into several pieces, perhaps one per memory module, and provide a separate lock for each. Thus, as many processes as pieces could simultaneously manipulate the map without interfering with one another

Initially the free blocks of each module would be unlinked, and grouped contiguously at a high address end of the module. Assignment of blocks would be sequential. Released blocks would be linked by absolute address into a chain. Further requests for block assignment are met by assigning the block at the head of the chain. Only when the chain for a module becomes empty are further blocks from the never-used portion of the module assigned.

## Project 4: Hash-coded system segment catalog search

This project is to replace the current linear search of the system segment catalog (of the storage management subsystem) with a faster hash-coded search. The search is performed each time the segment catalog manager is presented with a segment identifier which may or may not locate an entry in the catalog table. Because of the extreme length of this table, a failure of the linear search may usurp 10 or more seconds of processor time. A hash-coded search would allow success or failure to be determined in an average of two table references (assuming a half full table), greatly increasing the segment catalog manager's efficiency.

Appendix

## Project 5: Variable length descriptor segment and identifier table

Include in the process address space manager (of the storage management subsystem) a mechanism which allows the descriptor segment and identifier table of a process to vary in length as segments are added to or removed from the address space of the process. Currently, both are of fixed length, a practice which either limits the number of segments that may be in an address space or wastes memory, depending on whether they are too short or too long. A more ideal mechanism would automatically adjust the length to circumstances. Existing facilities of the SMS should be used to change the physical length of the segments.

Appendix

# Project 6: Variable length directory segments

This project is to modify the directory format (if necessary) and directory manipulator of the storage management subsystem so that the length of a directory will automatically be increased as branches and directory control list entries are added to it. Currently directories are of fixed length, and an error code is returned if a manipulation overflows the directory being manipulated. An extension of this project is to make directories shrink when branches and directory control list entries are removed. This is more difficult, for the remaining information seldom cooperates by grouping together at the beginning of the segment. Be sure to consider the possible consequence of chainging a directory segment's length in such a way as to alter its absolute base address.

Section A.1

Appendix

## Project 7: Return pointer entry point to the storage management subsystem

This project is to add a path through the SMS (which is callable by a user procedure from outside of ring zero) that will cause a segment to be removed from the address space of a process. The entry point in the user interface manager would be defined by the following CIMPL statement:

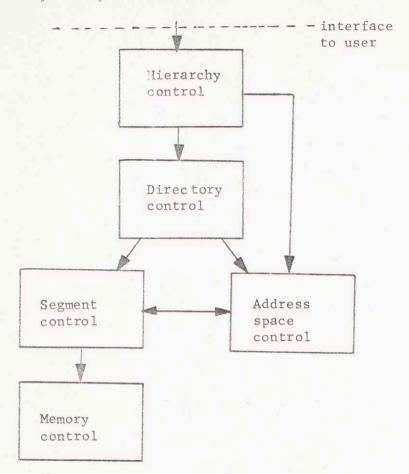

remove: entry (segptr pointer, validation\_level integer, RESULT bit);

The first argument is a pointer to some word of the segment to be removed, and the second is the validation level of the calling procedure. The user interface manager would, after appropriate argument manipulation and verification pass the call on to other modules lower in the SMS that would make certain the call to remove the segment comes from a ring at least as low as the ring from which the segment was included in the address space (record of this must be kept somewhere), and then remove the SDW and inform the segment catalog manager of the removal of the segment. If removal is successful then RESULT is returned "on". If unsuccessful, for any reason, then RESULT is returned "off".

# Project 8: Courteous segment deletion

This project is to alter the storage management subsystem so that a segment may be deleted in two ways: courteously or otherwise. The method currently used is the latter case - the deleted segment disappears immediately and is removed from the address spaces of all processes using it. Courteous deletion would allow processes currently using a segment to continue to do so, but would deny access to new processes. The last process removing the segment from its address space would cause it to be physically destroyed.

One method of implementation would include a courtesy switch in the argument list for the delete entry to the SMS. If "off" deletion would occur as it does now. If "on" then the segment's branch would immediately disappear from the hierarchy, but the system segment catalog entry would remain, suitably flagged, disappearing only when its use list became empty. Special problems may appear when courteous deletion is applied to directory segments?

Appendix

## Project 9: Immediately effective access control list changes

This project is to provide the option of making changes to the access control list of a segment immediately effective. Currently, alterations to an access control list have no effect on processes which already have a segment in their address spacer. For example, a change removing the access control list entry giving user A permission to cause his processes to read a segment would currently not affect user A's process which had the segment already in its address space at the time of the change. It would become effective only after user A's process gives the segment back. His processes would not be allowed further access, from that point on. The access control list alteration could be made immediately effective by setting the SDW fault bit in an affected process "on" and forcing the process to reinclude the segment in its address space, under the constraints of the new access control list. Which method of making the change to be used would be selected by inspecting a courtesy switch argument (caller provided). If "off" then the immediately effective method would be used. If "on" then the current (courteous) method would be used.

# Additional projects (not written up)

- 10. add symbolic links to the storage management subsystem hierarchy

- \*11. define a set of storage management subsystem driving commands (to operate in user ring)

- \*12. implement storage management subsystem commands

- \* Projects 11 and 12 need to be more closely defined. Specific commands should be suggested.

# Identification

Overview of hardware organization

#### Purpose

This section describes the overall organization of the hardware in the Clics system. The hardware and the control programs are highly functionally dependent, and the hardware has been designed to operate in the specific environment provided by the "software". Thus, hardware features must be viewed in conjunction with the associated control program environment.

# Introduction

The hardware system is organized as an interconnected group of modules. The most important kinds of modules are processors, I/O controllers, and memories. At any specific time, the number of each kind and the pattern of interconnection is fixed. Both, however, may vary over the life of the system. The use of many copies of a few basic modules, and a standard system-wide interconnection allows this variability of configuration in response to changing circumstances.

## Organization

The three major kinds of modules are divided into two groups: active and passive. The active modules (the processors and the I/O controllers) are characterized by their ability to execute instructions stored in a memory, while the passive modules (the memory modules) can only respond to externally applied commands.

Each major module has 16 ports (numbered 0-15) which are used to connect active modules to passive modules (An interconnection between an active and a passive module uses a single port on each.) Each active module is connected to each passive module. Each such interconnection is a single instance of the "major module interface".

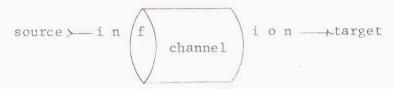

Active modules operate independently of each other and may communicate only with passive modules. An active module requests access to a specific passive module, and this request is granted asynchronously according to a prewired priority scheme. Communication between active modules is accomplished by first passing the message to a specific passive module, which then forwards the message to the second active module.

The hardware also includes two types of I/O devices: magnetic recording tape handlers and typewriter terminals. Each such device is directly connected to a specific I/O controller (perhaps via a switching network). The connection is called the "tape handler device interface" or the "typewriter terminal device interface".

## Identification

Major module interface

## Purpose

The major module interface provides the standard interconnection for all active and passive modules in the hardware system. By this interface a port on each active module (i.e. each processor or I/O controller) is connected to a port on each passive module (i.e., each memory module) in the system. Thus, in a system with m active modules and n passive modules there would be m times n instances of the major module interface.

### Introduction

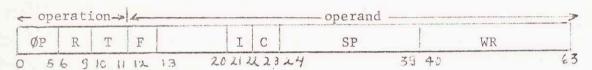

Each instance of the major module interface consists of 112 lines, arranged in 7 groups. The following table lists these groups, the number of lines in each, and the direction of communication.

| group name          | number of lines | direction of communication |

|---------------------|-----------------|----------------------------|

| data                | 64              | either                     |

| memory address      | 40              | active to passive          |

| command             | 3               | active to passive          |

| access request      | 1               | active to passive          |

| operation completed | 1               | passive to active          |

| final status        | 2               | passive to active          |

| interrupt present   | 1               | passive to active          |

## Data lines

The 64 data lines communicate a single word of information in either direction. If the command implies data movement from active to passive, such as it would for an operation storing a word in memory, then the data lines carry the information in that direction. If movement in the other direction is implied, such as for an operation reading a word from memory, then the data lines carry the word in the opposite direction. For any given command, however, communication via these lines occurs in one direction only.

# Memory address lines

The 40 memory address lines carry from the active module to the passive module the absolute address of the memory location to be referenced.

# Command lines

The 3 command lines carry from the active module to the passive module the code indicating the specific operation being requested of the passive module. The following table lists the legal commands, and indicates the direction of information flow over the data lines for each command.

| command            | mnemonic | code | data communication |

|--------------------|----------|------|--------------------|

| read               | READ     | 001  | passive to active  |

| write              | WRITE    | 010  | active to passive  |

| read and hold      | RAH      | 011  | passive to active  |

| set interrupt cell | SIC      | 100  | active to passive  |

| execute interrupt  | EXI      | 101  | passive to active  |

All unassigned codes result in the response "illegal action". (See below, final status lines.) The section of the notebook describing the memory modules indicates the specific response to each of these commands.

### Access request line

Once an active module has set the data, address, and command lines with the signals specifying the operation desired, a signal is placed on the access request line to indicate to the connected passive module that service is desired. The signal remains until the operation is completed and the results noted by the active module.

### Operation completed line

When the requested operation is completed, the passive module places a

signal on the operation completed line to inform the initiating active module that all output lines are set.

### Final status lines

The 2 <u>final status</u> lines return to the active module the termination state of the operation. The following table lists the possible states and the associated codes.

| state                            | code |

|----------------------------------|------|

| operation successfully completed | 00   |

| non-existent address             | 01   |

| parity error                     | 10   |

| illegal operation was requested  | 11   |

## Interrupt present line

The interrupt present line is a manifestation of the inter module control communication facility of the hardware system. A passive module sets a signal on this line to its control module when the interrupt cell in the passive module is set by an active module. See the notebook section on control communication for further description and references.

#### Communication

A typical use of the major module interface originates in an active module. Consider the example of writing a word into memory. Once the data is generated by a processor and the absolute address in which it is to be stored is computed, the port selection logic of the processor determines which of the 16 processor ports is connected to the memory module containing the desired address. The data and the address are set on the data and address lines, and the code for the command WRITE is set on the command lines. A signal is then set on the access request line.

The memory module connected to the selected port will complete service on requests from all lower numbered memory module ports, and then recognize the signal from this active module on the access request line. The indicated command is then performed.

When the storing operation is completed by the memory module, the final status lines are set by the memory module to indicate the outcome (assuming everything worked, they are set to 00) and a signal is set on the operation completed line. The final status and operation completed line signals remain until the access request signal from the processor initiating the action is removed, indicating that the output has been received and processed.

It is also possible for passive modules to initiate communication with active modules at the request of other active modules. Such is the case when the interrupt cell in a passive module is set in response to an SIC command to the passive module

Section C.O.02

Date: NFC 1.6 1968

### Identification

Control communication

#### Purpose

The active modules of the hardware system communicate with each other through the standard major module interface to the passive modules. The passive modules act as messengers, passing along communications received to the proper active module. This section describes the overall scheme of interrupt communication. The specific details, as they apply to the three kinds of modules involved, are given in the sections for those modules.

#### Introduction

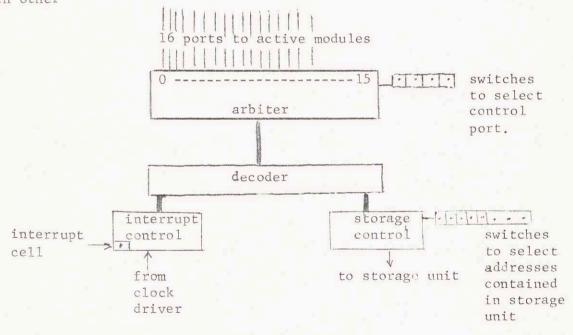

As previously described, each active module is connected to each passive module through the standard major module interface. The connections are to 16 ports on each module. One of these ports on each passive module is designated by switch setting as the control port for that memory. The processor or I/O controller connected to the control port is the control module associated with the passive module. In a normal system configuration each active module is the control module for at least one memory module, and there are at least as many passive as active modules.

When a passive module receives a control communication, called an interrupt, from any of the up to 16 active modules connected to it, it always forwards this message to its control module. Thus, in order for one active module (A) to send an interrupt to another (B), the passive module (C) controlled by B must be known by the number of the port on A connecting A to C.

#### Interrupts

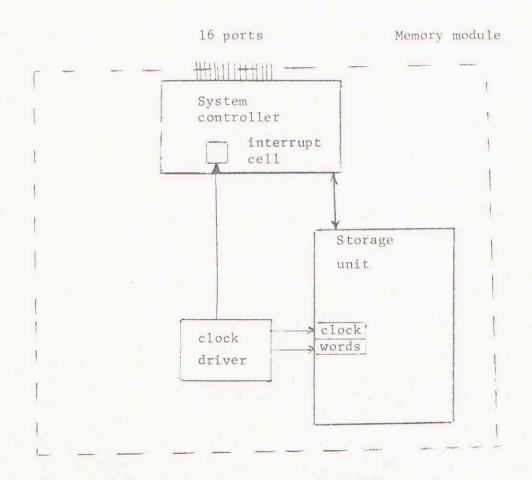

Contained in each passive module (in the system controller portion of the memory module) is an interrupt cell. This cell may be set by any active module by sending the command SIC to the memory module. When the cell is set the interrupt present line to the control module for the memory module is set with the signal. When next convenient, the control module will recognize the signal on this line, and request access to the passive module, indicating the command EXI (execute interrupt). The passive module will then respond by setting the cell "off" and removing the signal from the interrupt present line. The response of the active module to executed interrupts depends on whether the active module is a processor or an I/O controller. Processors make an unconditional CALL to the location specified by a special program loadable register. I/O controllers retrieve an instruction word from a prespecified memory location. See the descriptions of each of these modules for the details of their reaction.

6.233 Clics System Specification Notebook

Section C.0.03

Date: **DEC** 1 6 1968

## Identification

Tape device interface

## Purpose

The tape device interface is used to connect each magnetic recording tape handler to a specific I/O controller. The details of this interface are not contained in this version of the Clics notebook.

Section C.O.04

Date: DEC 1 6 1968

# Identification

Typewriter terminal device interface

### Purpose

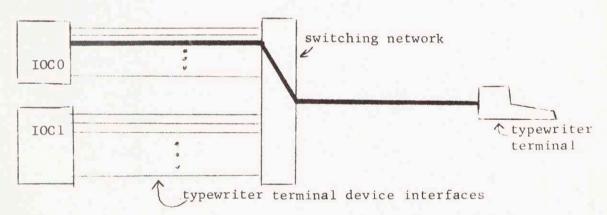

The typewriter terminal device interface is used to connect each type-writer terminal directly to a specific IOC, or to connect output taps from a switching network directly to a specific IOC. In the latter case, the typewriter terminals are attached to the input taps of the switching network. The details of this interface are not contained in this version of the Clics notebook.

Date: DEC 1 6 1968

#### Identification

Hardware configuration

## Purpose

In this section the hardware configuration of the current Clics system is specified. This configuration is not maximal, allowing for future expansion if circumstances warrant such growth.

### Specification of modules

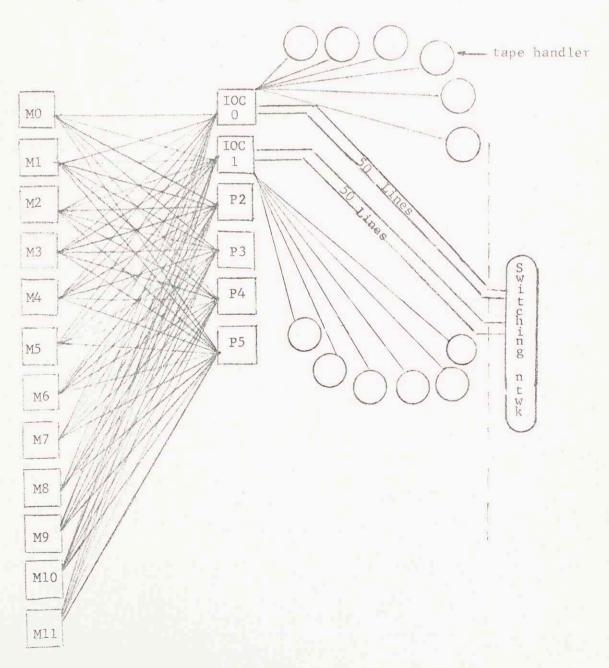

The current configuration includes the following modules and devices:

4 processors

2 input/output controllers

12 memory modules, two of which contain clocks

12 tape handlers

100 typewriter terminal lines from typewriter terminal switching network

The processors are labelled P2, P3, P4, and P5. The input/output controllers are labelled IOCO and IOC1. The memory modules are labelled MO through M11.

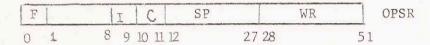

Each input/output controller contains 6 data channels for tape handlers (channels 3, 5, 7, 9, 11, and 13) and 50 data channels for typewriter terminals (channels 15, 17, ... 113).

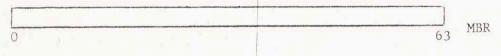

Memory modules MO through M11 contain in consecutive order locations O through 805,306,367. Each memory module contains an equal amount of storage.

#### Port assignments

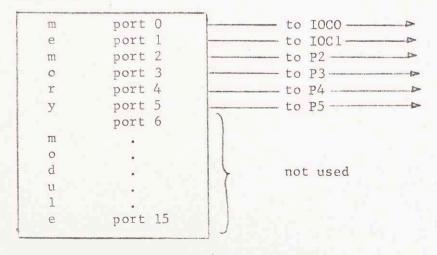

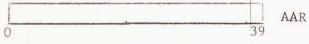

The following diagram indicates the port assignments for each of the 12 memory modules.

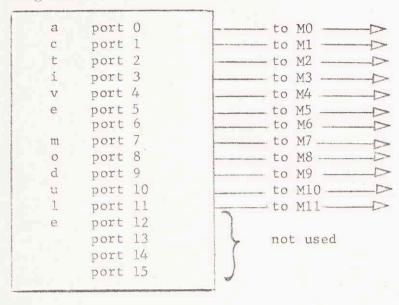

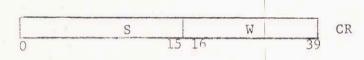

The port assignments for the active modules are indicated by the following diagram:

### Control relationships

IOCO, IOC1, P2, P3, P4, and P5 are the control modules for M0, M1, M2, M3, M4, and M5, respectively. Memory modules M6 through M1l do not require control modules.

#### Clocks

The primary system clock is contained in memory module M4. The backup system clock is contained in memory module M5. The following table indicates the address by which each may be referenced.

| clock                             | address (in decimal)       |

|-----------------------------------|----------------------------|

| primary calendar<br>primary alarm | 268,435,456<br>268,435,457 |

| secondary calendar                | 335,544,320                |

| secondary alarm                   | 335,544,321                |

The locations specified are the first two in M4 and M5.

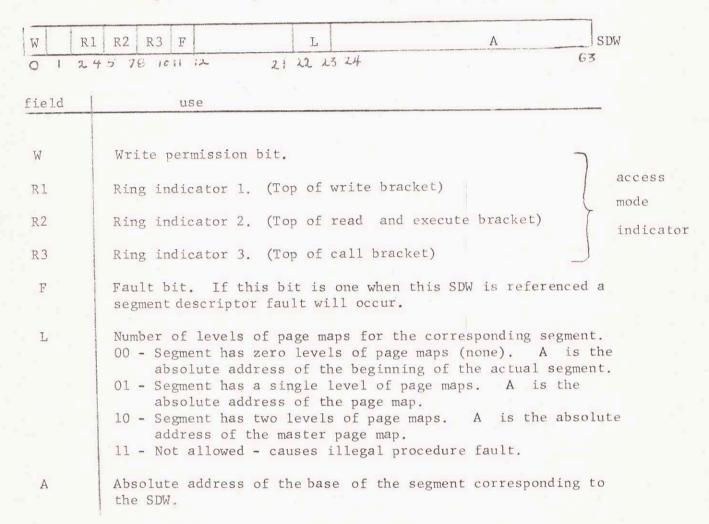

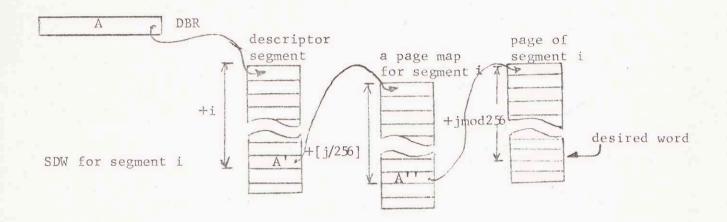

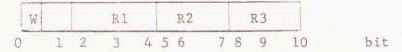

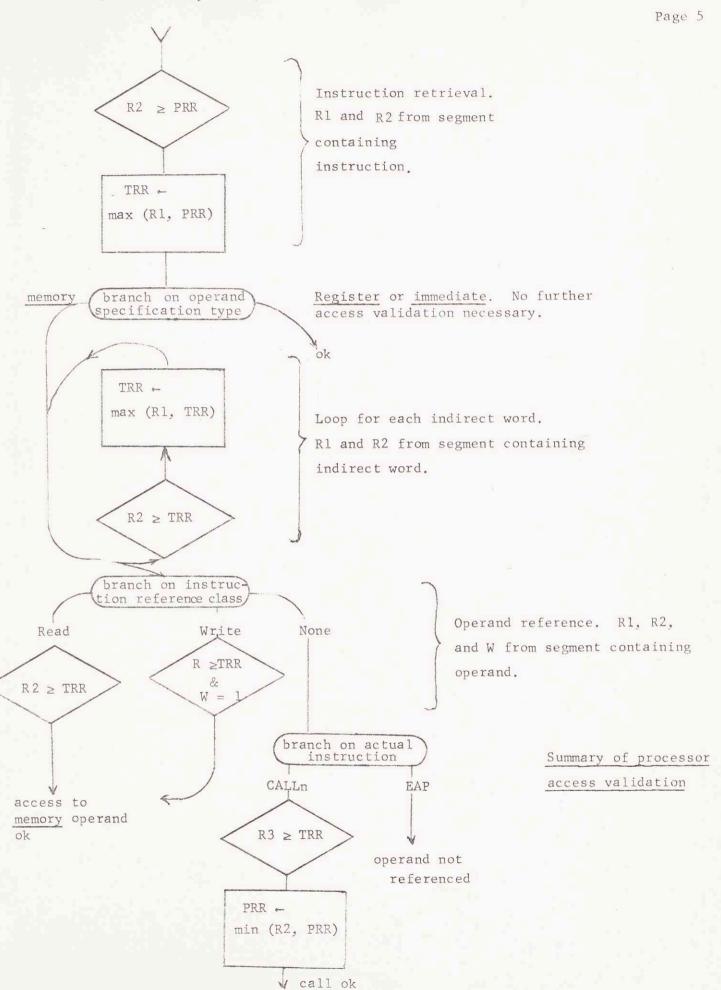

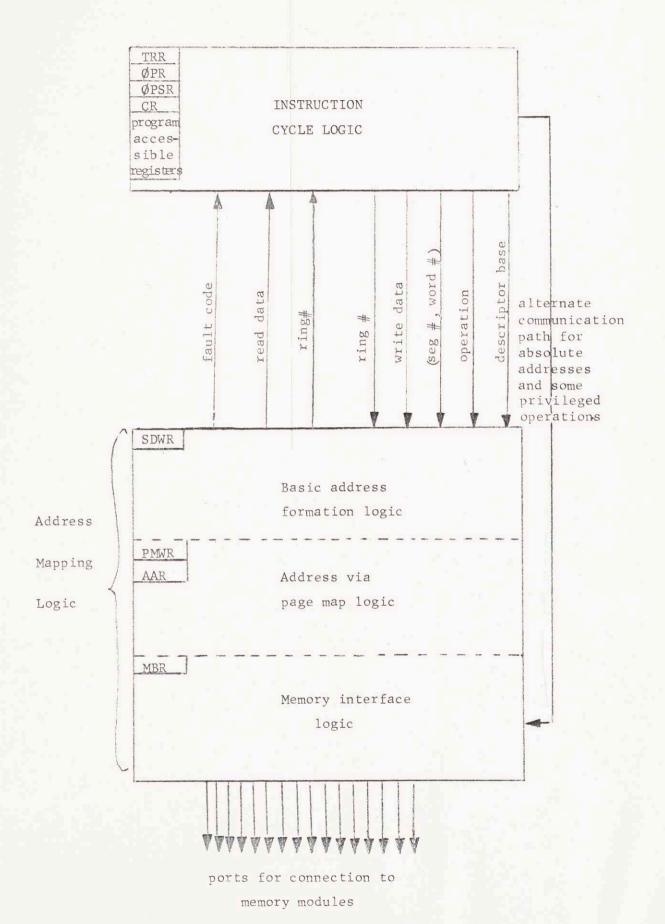

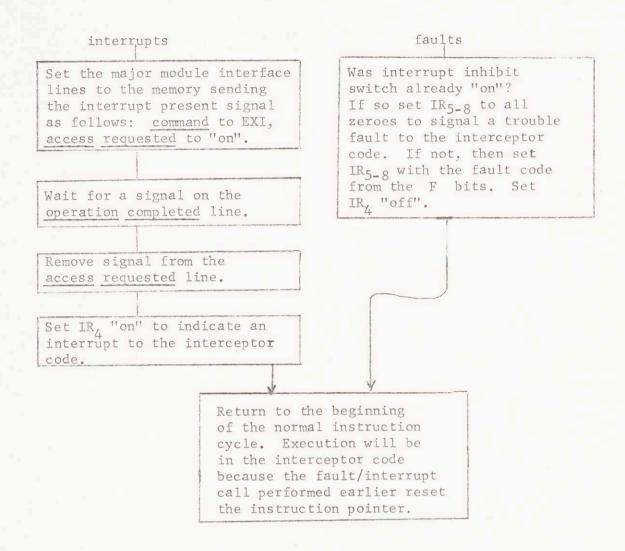

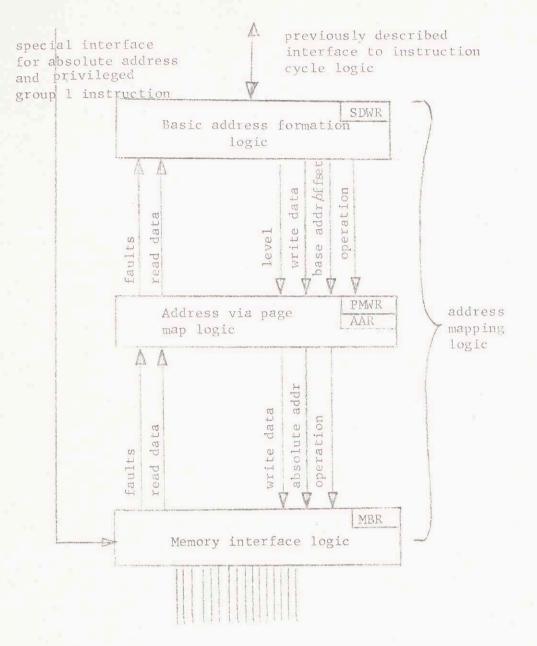

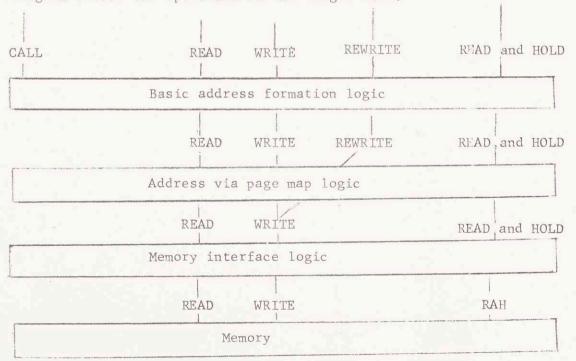

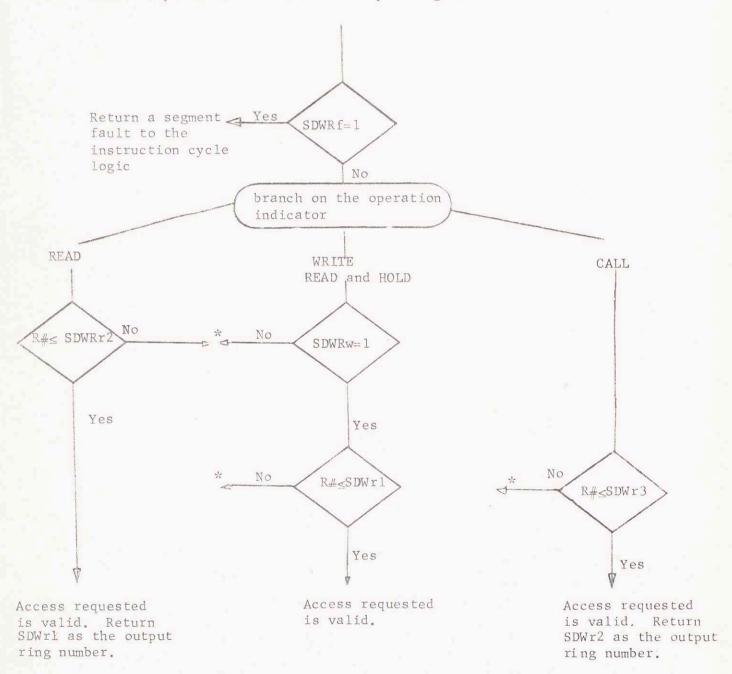

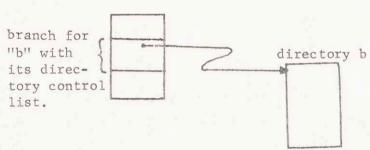

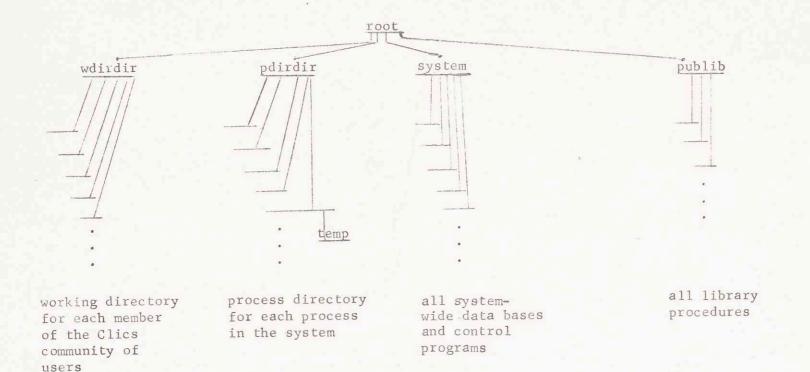

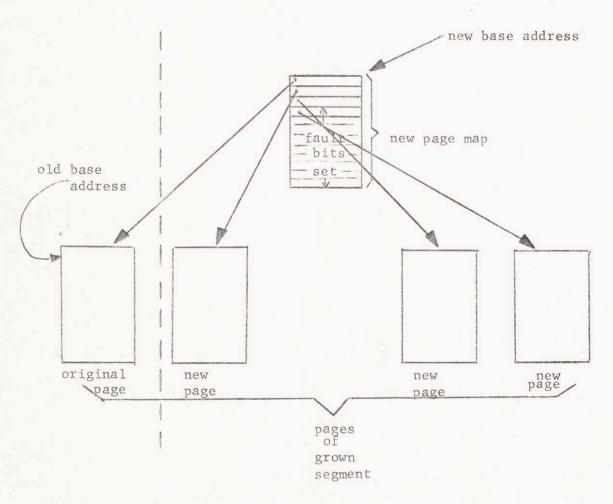

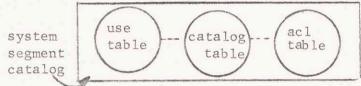

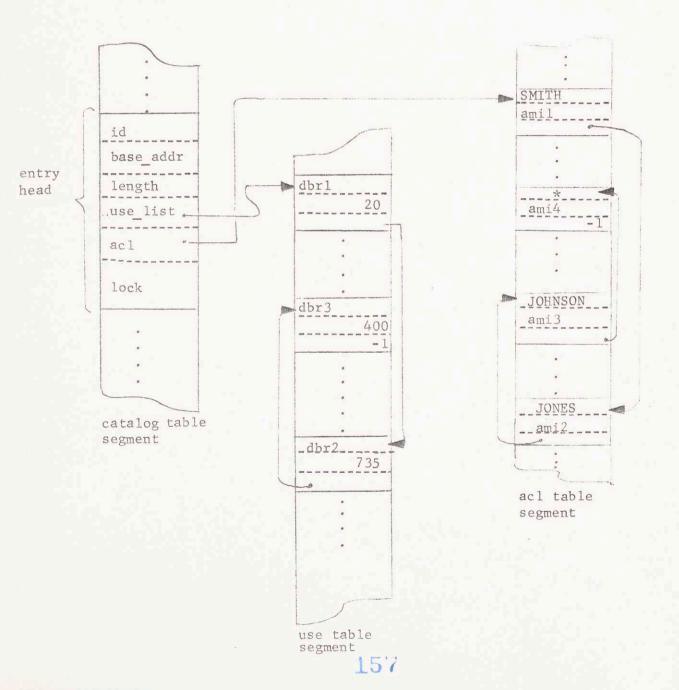

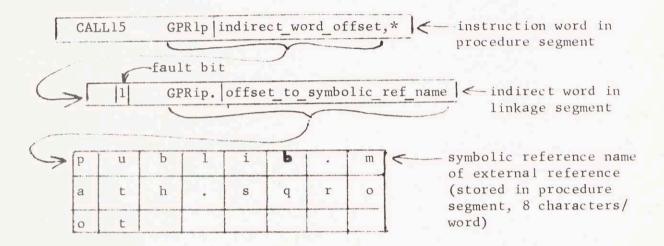

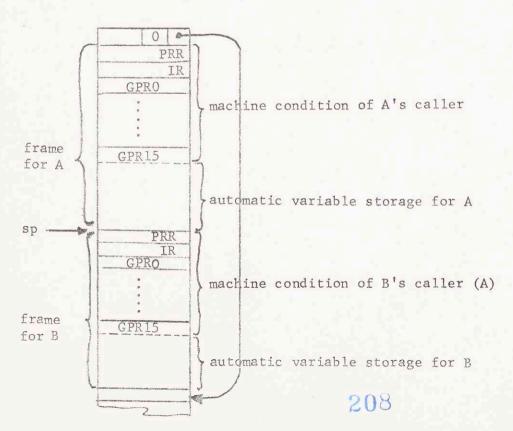

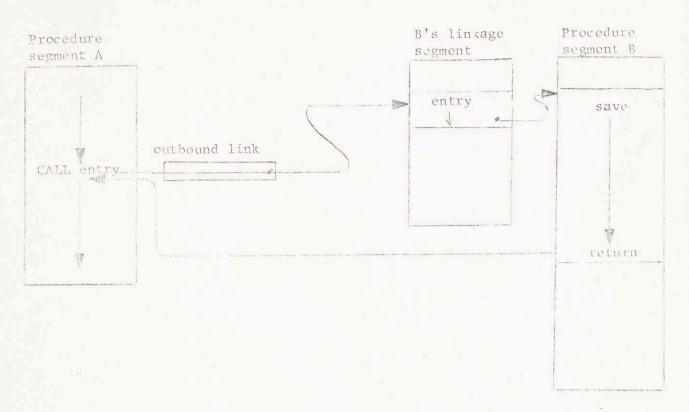

### Interrupt communication